Phase 3 - PLC Optimisation -

Today's Tasks

- Optimising "ALS_StepEngine"

Optimising "ALS_StepEngine"

Notes:

RaiseLevelInCIP..FC contains references to"T001_Steps".LevelRaise.Step[x], where x is an integer indexSWFlush..FB contains references to"T001_Steps".SWFlush.Step[x], where x is an integer index

Blocks contain "T001_Step".ppppp.Step._xxxx

FB's

GeneralPhasesEmptySteamBarriersMaintenanceAerationSelectAerationSIPSeq1AerationSIPSeq2AerationSIPSeq3AerationProductCoolAerationProductXferAerationCIPAirationShutdownAerationBarrierCoolAerationSteamBarrier_TempGuardsAgitationCIPShutdownSWFlushXferInlet1Sterilization_OtherFaults_TankPressure

In SCL

_LevelFaults

FC's

OutMotorsOut_Ster_signalsOut_Filler_Signals_GastiOut_Filler_Signals_AmpakOP_SignalsAerationOut_Aeration_SignalsCopyOutputFIC505GeneralOut_ValvesGeneralHMIHandlingAgitspeedPIC430LIC525PumpUnitSpeedEndVclStepsFillEmptyStepsCIPFlipStepsCIPISBStepsRaiseLevelInCIPSterProdISBMixOutletStepsPIC420

UDT Updates

To enable the en-mass update of actual block parameters, all the current compile errors were temporarily "commented-out" with the following phase Commented Out to Compile . This was to allow the commented out sections of code in a project search.

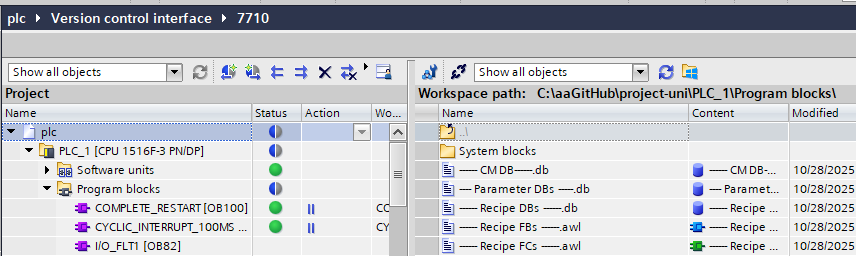

Version control interface

Once there were no compile errors source code of all "PLC data types", "PLC tags","programs blocks","Software units" and

"Technology objects" was generated by employing the Version control interface.

The source code files were then opened in JetBrains Intellij Ideal Ultimate, where the appropriate UDT files were edited . These are shown below;

_USR_Shutdown

TYPE "_USR_ShutDown"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[500..504] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

Comments are not contained in the source code of the UDT.

_USR_Sterilization

TYPE "_USR_Sterilization"

VERSION : 0.2

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[100..119] of Bool := [TRUE];

END_STRUCT;

BEGIN

END_TYPE

- Program blocks find/replaced

_USR_XferInlet1

TYPE "_USR_XferInlet1"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[200..222] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_EndVCL

TYPE "_USR_EndVCL"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[300..309] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_CIP

TYPE "_USR_CIP"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[600..630] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_Filling

TYPE "_USR_Filling"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[1000..1101] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_Agitation

TYPE "_USR_Agitation"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[3000..3004] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_CIPflip

TYPE "_USR_CIPflip"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[700..724] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_ISBProdSter

TYPE "_USR_ISBProdSter"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[1800..1814] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_ISBCIP

TYPE "_USR_ISBCIP"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[800..803] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

_USR_MixOutlet

TYPE "_USR_MixOutlet"

VERSION : 0.1

STRUCT

"_" { ExternalAccessible := 'False'; ExternalVisible := 'False'; ExternalWritable := 'False'} : Array[1700..1703] of Bool := [TRUE];

END_STRUCT;

END_TYPE

- Program blocks find/replaced

Updating actual formal parameters

All usage of the modified UDT symbolic structure was then updated by employing the project wide "Find/Replace" feature of the Intellij IDE.

The following is an example, for the MixOulet steps, shows the regex patterns used to update the MixOutlet steps

actual parameters, in FBD/LAD blocks, across the project.

The Find regex pattern

<Symbol>

<Component Name="T001_Steps"/>

<Component Name="MixOutlet"/>

<Component Name="Step"/>

<Component Name="_(\d{1,})"/>

</Symbol>

The Replace regex pattern

<Symbol>

<Component Name="T001_Steps"/>

<Component Name="MixOutlet"/>

<Component Name="Step"/>

<Component Name="_"/>

<Access Scope="LiteralConstant">

<Constant>

<ConstantType>DInt</ConstantType>

<ConstantValue>$1</ConstantValue>

</Constant>

</Access>

</Component>

</Symbol>

The above patterns were adjusted for each top level tag in the T001_Steps Datablock.

Since the number usage of Step bits in SCL blocks were minimal these were manually updated.

Importing source code.

After modification were complete in the source code these were imported and synchronized back into TIA via the VCI.

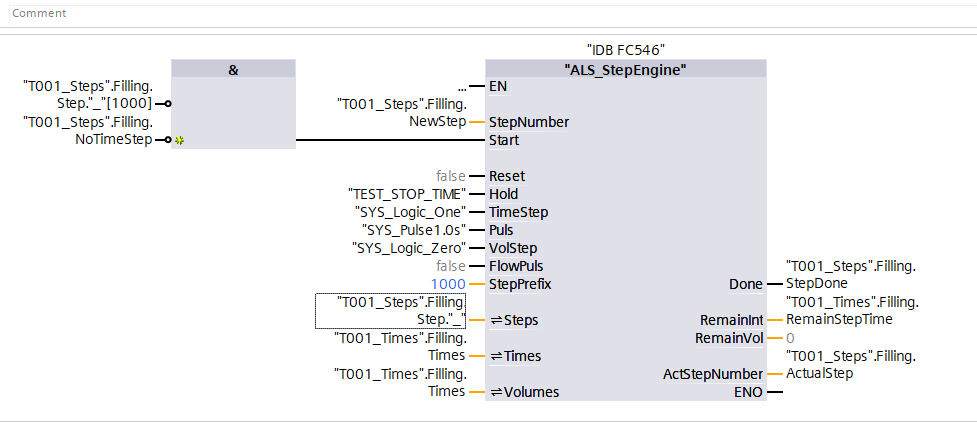

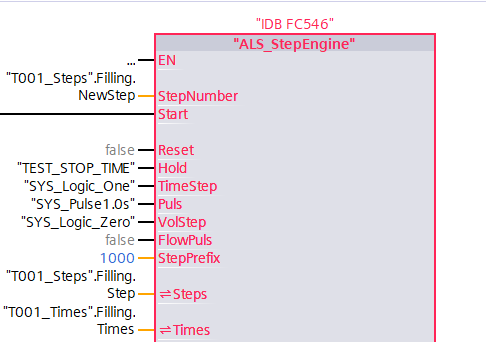

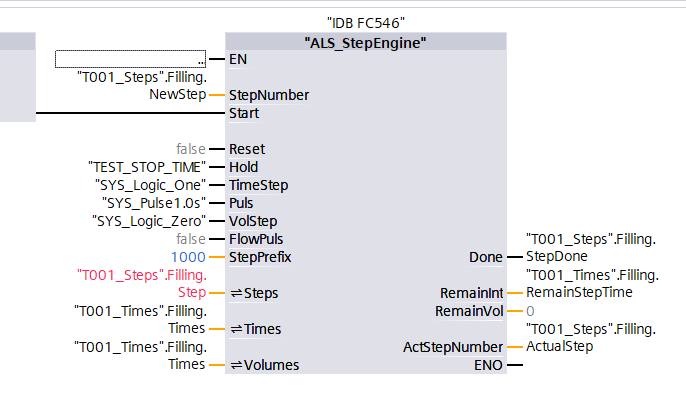

Subsequent rebuild highlighted errors where the ALS_StepEngine block call required updating and the actual

parameter for the Steps formal parameter of the ALS_StepEngine function block required re-referencing to the boolean

array within the given UDT.

ALS_StepEngine "block call update" required

ALS_StepEngine actual parameter required update (before)

ALS_StepEngine actual parameter required update (after)